- Samsung to release 400-layer NAND chip for AI data centers

- New BV NAND tech boosts density and minimizes heat buildup

- Plans for 1,000-layer NAND by 2030 to expand capacity

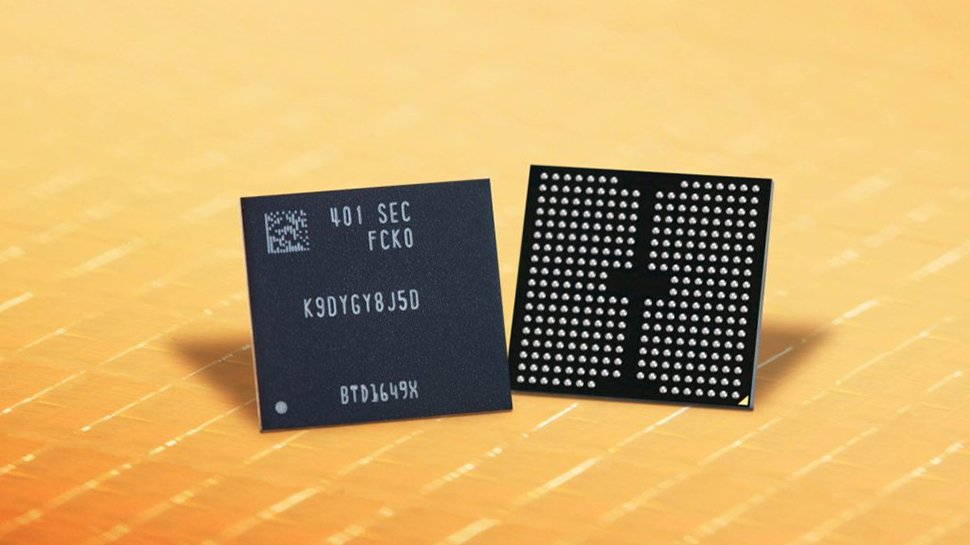

Samsung is working to launch a record-breaking 400-layer vertical NAND flash chip by 2026, reports have claimed.

A report by the Korea Economic Daily says Samsung’s Device Solutions (DS) division aims to advance the NAND flash market with its cutting-edge V10 NAND, designed to meet surging demand in AI data centers.

The company’s memory roadmap, as outlined in the report, shows plans for an advanced 10th-generation NAND that will utilize bonding technology to separately build memory cells and the peripheral circuitry on different wafers, later fusing them into a single chip. Known as bonding vertical NANDFlash (BV NAND), this new approach minimizes heat buildup and maximizes both capacity and performance, creating what Samsung has described as a “dream NAND for AI.”

1,000 layers by 2030

The BV NAND design, boasting a 1.6x increase in bit density per unit area, supports ultra-high-capacity solid-state drives (SSDs) ideal for AI applications.

Samsung’s current 286-layer V9 NAND chips marked a significant milestone, but the 400-layer V10 is expected to redefine capacity limits, potentially breaking the 200TB storage threshold for ultra-large AI hyperscaler SSDs, while improving energy efficiency.

For future releases, world’s largest memory chipmaker plans to introduce 11th-generation V11 NAND in 2027 with a 50% faster data transfer speed, further optimizing performance for high-demand data storage needs.

Samsung’s ambitious NAND roadmap extends even further, with plans for chips exceeding 1,000 layers by 2030, KED reports. This advancement aims to keep Samsung at the forefront of the high-capacity NAND market, where demand is spurred by AI applications that require expansive storage solutions to process vast volumes of data.

In the DRAM sector, Samsung aims to release sixth-generation 1c DRAM and seventh-generation 1d DRAM by the end of 2024, targeting use in high-performance AI chips. According to the Korea Economic Daily report, the company also has plans for sub-10 nm 0a DRAM by 2027, using a vertical channel transistor structure for greater stability and efficiency.

You might also like

This articles is written by : Nermeen Nabil Khear Abdelmalak

All rights reserved to : USAGOLDMIES . www.usagoldmines.com

You can Enjoy surfing our website categories and read more content in many fields you may like .

Why USAGoldMines ?

USAGoldMines is a comprehensive website offering the latest in financial, crypto, and technical news. With specialized sections for each category, it provides readers with up-to-date market insights, investment trends, and technological advancements, making it a valuable resource for investors and enthusiasts in the fast-paced financial world.