Andrae, A. S. G. & Edler, T. On international electrical energy utilization of communication know-how: developments to 2030. Challenges 6, 117–157 (2015).

Jones, N. Methods to cease knowledge centres from gobbling up the world’s electrical energy. Nature 561, 163–166 (2018).

IRDS. Worldwide Roadmap for Gadgets and Techniques IRDS. IEEE https://irds.ieee.org (2023).

Manipatruni, S., Nikonov, D. E. & Younger, I. A. Past CMOS computing with spin and polarization. Nat. Phys. 14, 338–343 (2018).

Sharma, V. & Rajawat, A. Assessment of approaches for radiation hardened combinational logic in CMOS silicon know-how. IETE Tech. Rev. 35, 562–573 (2018).

Fanghui, R., Jander, A., Dhagat, P. & Nordman, C. Radiation tolerance of magnetic tunnel junctions with MgO tunnel obstacles. IEEE Trans. Nucl. Sci. 59, 3034–3038 (2012).

Hughes, H. et al. Radiation research of spin-transfer torque supplies and units. IEEE Trans. Nucl. Sci. 59, 3027–3033 (2012).

Alamdar, M. et al. Irradiation results on perpendicular anisotropy spin–orbit torque magnetic tunnel junctions. IEEE Trans. Nucl. Sci. 68, 665–670 (2021).

Bennett, C. H. et al. Radiation response of domain-wall magnetic tunnel junction logic units. IEEE Trans. Nucl. Sci. 71, 454–460 (2024).

Mochizuki, A., Kimura, H., Ibuki, M. & Hanyu, T. TMR-based logic-in-memory circuit for low-power VLSI. IEICE Trans. Fundamentals Electron. Commun. Laptop Sci. 88, 1408–1415 (2005).

Gebregiorgis, A., Bishnoi, R. & Tahoori, M. B. Spintronic normally-off heterogenous system-on-chip design. In 2018 Design, Automation & Check in Europe Conf. & Exhibition (DATE) 113–118 (IEEE, 2018). This paper exhibits how a normally-off system on chip may be designed by a hybrid structure containing standard CMOS bistable parts in addition to totally different flavours of spintronic-based non-volatile storage parts.

Deng, E., Anghel, L., Prenat, G. & Zhao, W. Multi-context non-volatile content material addressable reminiscence utilizing magnetic tunnel junctions. In 2016 IEEE/ACM Int. Symp. Nanoscale Architectures 103–108 (IEEE, 2016). This text exhibits that content-addressable recollections may be made utilizing MTJs.

Jin, H. et al. Area wall-magnetic tunnel junction analog content material addressable reminiscence utilizing present and projected knowledge. IEEE Trans. Nanotechnol. 23, 20–28 (2024).

Iwai, H. Way forward for nano CMOS know-how. In twenty eighth Symp. Microelectronics Know-how and Gadgets (IEEE, 2013).

Radosavljevic, M. & Kavalieros, J. 3D-stacked CMOS takes Moore’s regulation to new heights. IEEE Spectrum 32–37 (IEEE, 2022).

Chang, C. H. et al. Important course of options enabling aggressive contacted gate pitch scaling for 3 nm CMOS know-how and past. In Technical Digest—Int. Electron Gadgets Assembly (IEDM) 623–626 (IEEE, 2022).

Chung, Y.-Y. et al. First demonstration of GAA monolayer-MoS2 nanosheet nFET with 410 μA μm ID 1V VD at 40 nm gate size. In Technical Digest—Int. Electron Gadgets Assembly (IEDM) 823–826 (IEEE, 2022).

Rupp, Ok. microprocessor-trend-data. GitHub https://github.com/karlrupp/microprocessor-trend-data (2022).

Zhang, Ok. et al. SRAM design on 65-nm CMOS know-how with dynamic sleep transistor for leakage discount. IEEE J. Stable-State Circuits 40, 895–900 (2005).

Tachibana, F. et al. A 27% lively and 85% standby energy discount in dual-power-supply SRAM utilizing BL energy calculator and digitally controllable retention circuit. IEEE J. Stable-State Circuits 49, 118–126 (2014).

Sabry Aly, M. M. et al. Vitality-efficient abundant-data computing: the N3XT 1,000×. Laptop 48, 24–33 (2015).

Singer, P. Scaling the BEOL: a toolbox crammed with new processes, boosters and conductors. Semiconductor Digest. https://www.semiconductor-digest.com/scaling-the-beol-a-toolbox-filled-with-new-processes-boosters-and-conductors/ (2020). This text exhibits that interconnect power dissipation is a dominant supply of power loss in trendy CPUs and recollections.

Prasad, D. & Naeemi, A. Interconnect design and know-how optimization for standard and rising nanoscale units: a bodily design perspective. In Technical Digest—Int. Electron Gadgets Assembly (IEDM) 5.1.1–5.1.4 (IEEE, 2018).

Dang, F., Solar, X. Ok., Bin Liu, Ok., Xu, Y. F. & Liu, Y. H. A survey on clock synchronization within the industrial web. J. Comput. Sci. Technol. 38, 146–165 (2023).

Likamwa, R., Hou, Y., Gao, Y., Polansky, M. & Zhong, L. RedEye: analog ConvNet picture sensor structure for steady cellular imaginative and prescient. In forty third Int. Symp. Laptop Structure (ISCA) 255–266 (IEEE, 2016).

Wilson, R. B. et al. Ultrafast magnetic switching of GdFeCo with digital warmth currents. Phys. Rev. B 95, 180409 (2017).

Guan, Y. et al. Ionitronic manipulation of current-induced area wall movement in artificial antiferromagnets. Nat. Commun. 12, 1–8 (2021).

Alam, S. M. et al. Versatile STT-MRAM structure for reminiscence and rising functions. In IEEE thirty fourth Magnetic Recording Conf. (TMRC) (IEEE, 2023).

Muller, J. et al. From emergence to prevalence: 22FDX® embedded STT-MRAM. In IEEE Worldwide Reminiscence Workshop (IMW) (2022).

Naik, V. B. et al. STT-MRAM product reliability and cross-talk. In IEEE Electron Gadgets Know-how and Manufacturing Conf. (EDTM) 366–368 (IEEE, 2022).

Jew, T. MRAM in microcontroller and microprocessor product functions. In Technical Digest—Int. Electron Gadgets Assembly (IEDM) 11.1.1–11.1.3 (IEEE, 2020).

Ross, A. et al. Multilayer spintronic neural networks with radiofrequency connections. Nat. Nanotechnol. 18, 1273–1280 (2023).

Sakhare, S. et al. Enablement of STT-MRAM as final degree cache for the excessive efficiency computing area on the 5nm node. In Technical Digest—Int. Electron Gadgets Assembly (IEDM) 18.3.1–18.3.4 (IEEE, 2018).

Kan, J. J. et al. A examine on virtually limitless endurance of STT-MRAM. IEEE Trans. Electron. Gadgets 64, 3639–3646 (2017).

Ikeda, S. et al. A perpendicular-anisotropy CoFeB–MgO magnetic tunnel junction. Nat. Mater. 9, 721–724 (2010).

Streetman, B. & Banerjee, S. Stable State Digital Gadgets, International Version (Pearson Training, 2015).

Rao, S. et al. A scientific evaluation of W-doped CoFeB single free layers for low energy STT-MRAM functions. Electronics 10, 2384 (2021).

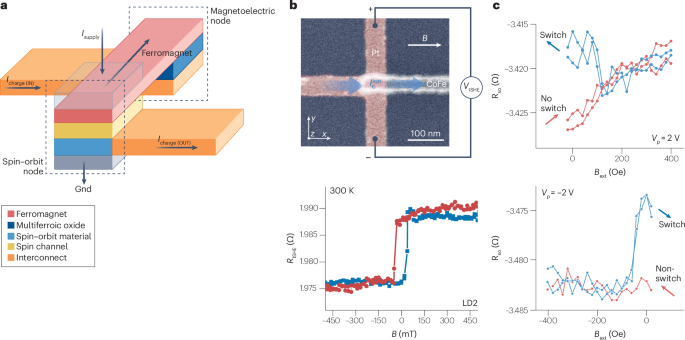

Manipatruni, S. et al. Scalable energy-efficient magnetoelectric spin–orbit logic. Nature 565, 35–42 (2019). This text introduces the proposal of MESO logic.

Nikonov, D. E. & Younger, I. A. Benchmarking of beyond-CMOS exploratory units for logic built-in circuits. IEEE J. Explor. Stable-State Comput. Gadgets Circuits 1, 3–11 (2015).

Fedorova, N. S., Nikonov, D. E., Li, H., Younger, I. A. & Íñiguez, J. First-principles Landau-like potential for BiFeO3 and associated supplies. Phys. Rev. B 106, 165122 (2022).

Fedorova, N. S. et al. Understanding magnetoelectric switching in BiFeO3 skinny movies. Phys. Rev. B 109, 085116 (2023).

Liu, H. et al. Synchronous circuit design with beyond-CMOS magnetoelectric spin-orbit units towards 100-mV logic. IEEE J. Explor. Stable-State Comput. Gadgets Circuits 5, 1–9 (2019).

Li, H., Lin, C. C., Nikonov, D. E. & Younger, I. A. Differential electrically insulated magnetoelectric spin–orbit logic circuits. IEEE J. Explor. Stable-State Comput. Gadgets Circuits 7, 18–25 (2021).

Li, H. et al. Physics-based fashions for magneto-electric spin–orbit logic circuits. IEEE J. Explor. Stable-State Comput. Gadgets Circuits 8, 10–18 (2022).

Liao, Y. C. et al. Evaluating the performances of the ultralow energy magnetoelectric random entry reminiscence with a physics-based compact mannequin of the antiferromagnet/ferromagnet bilayer. IEEE Trans. Electron. Gadgets 69, 2331–2337 (2022).

Rothe, R. et al. Vitality environment friendly logic and reminiscence design with beyond-CMOS magnetoelectric spin–orbit (MESO) know-how towards ultralow provide voltage. IEEE J. Explor. Stable-State Comput. Gadgets Circuits 9, 124–133 (2023).

Pham, V. T. et al. Spin–orbit magnetic state readout in scaled ferromagnetic/heavy steel nanostructures. Nat. Electron. 3, 309–315 (2020). This text presents experimental remark of spin–orbit detection of magnetic states.

Groen, I. et al. Disentangling spin, anomalous, and planar Corridor results in ferromagnet-heavy-metal nanostructures. Phys. Rev. Appl. 15, 044010 (2021).

Prasad, B. et al. Ultralow voltage manipulation of ferromagnetism. Adv. Mater. 32, 2001943 (2020).

Debashis, P. et al. Low-voltage and high-speed switching of a magnetoelectric component for power environment friendly compute. In Technical Digest—Int. Electron Gadgets Assembly (IEDM) 3641–3644 (IEEE, 2022).

Parsonnet, E. et al. Towards intrinsic ferroelectric switching in multiferroic BiFeO3. Phys. Rev. Lett. 125, 067601 (2020).

Vaz, D. C. et al. Voltage-based magnetization switching and studying in magnetoelectric spin–orbit nanodevices. Nat. Commun. 15, 1902 (2024). This text demonstrates the newest experimental advances for MESO logic.

Choi, W. Y. et al. All-electrical spin-to-charge conversion in sputtered BixSe1–x. Nano Lett. 22, 7992–7999 (2022).

Herling, F. et al. Gate tunability of extremely environment friendly spin-to-charge conversion by spin Corridor impact in graphene proximitized with WSe2. APL Mater. 8, 071103 (2020).

Currivan, J. A., Jang, Y., Mascaro, M. D., Baldo, M. A. & Ross, C. A. Low power magnetic area wall logic briefly, slender, ferromagnetic wires. IEEE Magn. Lett. 3, 3000104 (2012).

Zogbi, N. et al. Parallel matrix multiplication utilizing voltage-controlled magnetic anisotropy area wall logic. IEEE J. Explor. Stable-State Comput. Gadgets Circuits. 9, https://doi.org/10.1109/jxcdc.2023.3266441 (2023). This work exhibits the high-performance compute functionality and prospects for DW-MTJ logic, in addition to a path in the direction of lower-energy voltage management.

Alamdar, M. et al. Area wall–magnetic tunnel junction spin–orbit torque units and circuits for in-memory computing. Appl. Phys. Lett. 118, 112401 (2021). This text presents an experimental demonstration of DW-MTJ units and small circuits, working with spin–orbit torque and electrically nucleated area partitions.

Xiao, T. P. et al. Vitality and efficiency benchmarking of a site wall–magnetic tunnel junction multibit adder. IEEE J. Explor. Stable-State Comput. Gadgets Circuits 5, 188–196 (2019).

Morris, D., Bromberg, D., Zhu, J. & Pileggi, L. mLogic: ultra-low voltage non-volatile logic circuits utilizing STT-MTJ units. In DAC Design Automation Conf. 486–491 (IEEE, 2012).

Jouppi, N. P. et al. In-datacenter efficiency evaluation of a tensor processing unit. In Proc. forty fourth Annual Int. Symp. Laptop Structure 1–12 (2017).

Currivan-Incorvia, J. A. et al. Logic circuit prototypes for three-terminal magnetic tunnel junctions with cellular area partitions. Nat. Commun. 7, 10275 (2016).

Liu, S. et al. A site wall–magnetic tunnel junction synthetic synapse with notched geometry for correct and environment friendly coaching of deep neural networks. Appl. Phys. Lett. 118, 202405 (2021).

Liu, S. et al. Bayesian neural networks utilizing magnetic tunnel junction-based probabilistic in-memory computing. Entrance. Nanotechnol. 4, 1092820 (2022).

Leonard, T. et al. Form-dependent multi-weight magnetic synthetic synapses for neuromorphic computing. Adv. Electron. Mater. 8, 2200563 (2022). This work presents experimental DW-MTJs exhibiting excessive management of the DW place.

Leonard, T., Liu, S., Jin, H. & Incorvia, J. A. C. Stochastic area wall–magnetic tunnel junction synthetic neurons for noise-resilient spiking neural networks. Appl. Phys. Lett. 122, 26 (2023).

Cui, C., Liu, S., Kwon, J. & Incorvia, J. A. C. Area wall magnetic tunnel junction dependable combine and fireplace neuron. Preprint at https://arxiv.org/abs/2405.14851 (2024).

Nikonov, D. E., Bourianoff, G. I. & Ghani, T. Proposal of a spin torque majority gate logic. IEEE Electron. System Lett. 32, 1128–1130 (2011).

Raymenants, E. et al. Nanoscale area wall units with magnetic tunnel junction learn and write. Nat. Electron. 4, 392–398 (2021). This text presents vital experiments on electrical management of area partitions for STMGs and DW-MTJs.

Vaysset, A. et al. Towards error-free scaled spin torque majority gates. AIP Adv. 6, 065304 (2016).

Yang, S. H., Ryu, Ok. S. & Parkin, S. Area-wall velocities of as much as 750 m s–1 pushed by exchange-coupling torque in artificial antiferromagnets. Nat. Nanotechnol. 10, 221–226 (2015).

Bhattacharya, D. et al. 3D interconnected magnetic nanowire networks as potential built-in multistate memristors. Nano Lett. 22, 10010–10017 (2022).

Becherer, M. et al. A monolithic 3D built-in nanomagnetic co-processing unit. Stable. State Electron. 115, 74–80 (2016). This work provides a transparent path in the direction of 3D integration of field-coupled NML, summarizing the essential constructing blocks for a digital co-processing unit.

Becherer, M. 3D nanomagnetic logic. In Rising Non-Risky Reminiscence Applied sciences (eds Lew, W. S. et al.) 3–438 (Springer Nature Restricted, 2021).

Hassan, N. et al. Safe logic locking with strain-protected nanomagnet logic. In ACM/IEEE Design Automation Conf. (DAC) 127–132 (IEEE, 2021).

Edwards, A. J. et al. Bodily and algorithmically safe logic locking with hybrid CMOS/nanomagnet logic circuits. In Proc. 2022 Conf. Exhibition on Design, Automation & Check in Europe 17–22 (IEEE, 2022).

Breitkreutz, S. et al. Compact modeling of perpendicular nanomagnetic logic primarily based on threshold gates. J. Appl. Phys. 115, 17–104 (2014).

Turvani, G., Riente, F., Plozner, E., Schmitt-Landsiedel, D. & Gamm, S. B. V. A compact bodily mannequin for the simulation of pNML-based architectures. AIP Adv. 7, 56005 (2017).

Žiemys, G. et al. Modeling and simulation of nanomagnetic logic with cadence virtuoso utilizing Verilog-A. Stable. State Electron. 125, 247–253 (2016).

Garlando, U. et al. Architectural exploration of perpendicular nano magnetic logic primarily based circuits. Integration 63, 275–282 (2018).

Riente, F. et al. MagCAD: instrument for the design of 3-D magnetic circuits. IEEE J. Explor. Stable-State Comput. Gadgets Circuits 3, 65–73 (2017).

Riente, F. et al. ToPoliNano: a CAD instrument for nano magnetic logic. IEEE Trans. Comput. Des. Integr. Circuits Syst. 36, 1061–1074 (2017).

Bhoi, B. Ok., Misra, N. Ok. & Pradhan, M. Synthesis and simulation examine of non-restoring cell structure structure in perpendicular nano-magnetic logic. J. Comput. Electron. 19, 407–418 (2020).

Kiermaier, J. et al. Data transport in field-coupled nanomagnetic logic units. J. Appl. Phys. 113, 17B902 (2013).

Eichwald, I. et al. Nanomagnetic logic: error-free, directed sign transmission by an inverter chain. IEEE Trans. Magn. 48, 4332–4335 (2012).

Breitkreutz, S. et al. Nanomagnetic logic: demonstration of directed sign circulate for field-coupled computing units. In European Stable-State System Analysis Conf. 323–326 (IEEE, 2011).

Breitkreutz, S. et al. Managed reversal of Co/Pt dots for nanomagnetic logic functions. J. Appl. Phys. 111, 07A715 (2012).

Breitkreutz, S. et al. Majority gate for nanomagnetic logic with perpendicular magnetic anisotropy. IEEE Trans. Magn. 48, 4336–4339 (2012).

Papp, A. et al. Threshold gate-based circuits from nanomagnetic logic. IEEE Trans. Nanotechnol. 13, 990–996 (2014).

Breitkreutz, S. et al. 1-Bit full adder in perpendicular nanomagnetic logic utilizing a novel 5-input majority gate. EPJ Internet Conf. 75, 05001 (2014).

Eichwald, I. et al. Sign crossing in perpendicular nanomagnetic logic. J. Appl. Phys. 115, 17–510 (2014).

Eichwald, I. et al. Majority logic gate for 3D magnetic computing. Nanotechnology 25, 335202 (2014).

Ziemys, G. et al. Characterization of the magnetization reversal of perpendicular nanomagnetic logic clocked within the ns-range. AIP Adv. 6, 56404 (2016).

Mendsich, S., Ahrens, V., Kiechle, M., Papp, A. & Becherer, M. Perpendicular nanomagnetic logic primarily based on low anisotropy CoNi multilayer. J. Magn. Magn Mater. 510, 166626 (2020).

Mendisch, S. et al. Controlling domain-wall nucleation in Ta/Co–Fe–B/MgO nanomagnets through native Ga+ ion irradiation. Phys. Rev. Appl. 16, 014039 (2021).

Favaro, D. et al. Enabling logic computation between Ta/CoFeB/MgO nanomagnets. IEEE Trans. Magn. 59, 1–10 (2023).

Khitun, A., Kang, Wang, L. & Wang, Ok. L. Non-volatile magnonic logic circuits engineering. J. Appl. Phys. 110, 34306 (2011).

Mahmoud, A. et al. Introduction to spin wave computing. J. Appl. Phys. 128, 161101 (2020).

Chumak, A. V., Vasyuchka, V. I., Serga, A. A. & Hillebrands, B. Magnon spintronics. Nat. Phys. 11, 453–461 (2015).

Kostylev, M. P., Serga, A. A., Schneider, T., Leven, B. & Hillebrands, B. Spin-wave logical gates. Appl. Phys. Lett. 87, 1–3 (2005).

Lee, Ok. S. & Kim, S. Ok. Conceptual design of spin wave logic gates primarily based on a Mach–Zehnder-type spin wave interferometer for common logic capabilities. J. Appl. Phys. 104, 53909 (2008).

Kostylev, M. P., Serga, A. A., Schneider, T., Leven, B. & Hillebrands, B. Principle of dipole-exchange spin wave spectrum for ferromagnetic movies with combined alternate boundary circumstances. J. Phys. C: Stable. State Phys. 19, 7013 (1986).

Ciubotaru, F., Devolder, T., Manfrini, M., Adelmann, C. & Radu, I. P. All electrical propagating spin wave spectroscopy with broadband wavevector functionality. Appl. Phys. Lett. 109, 12403 (2016).

Klingler, S. et al. Design of a spin-wave majority gate using mode choice. Appl. Phys. Lett. 105, 152410 (2014).

Mahmoud, A. et al. Spin wave primarily based full adder. In Proc. IEEE Int. Symp. Circuits and Techniques 1–5 (IEEE, 2021).

Mahmoud, A. N. et al. A spin wave-based approximate 4:2 compressor: looking for essentially the most energy-efficient digital computing paradigm. IEEE Nanotechnol. Magazine. 16, 47–56 (2022).

Zografos, O. et al. Design and benchmarking of hybrid CMOS-Spin Wave System Circuits in comparison with 10nm CMOS. In Int. Conf. Nanotechnology 686–689 (IEEE, 2015).

Mahmoud, A. et al. Would Magnonic Circuits Outperform CMOS Counterparts? In Proc. ACM Nice Lakes Symp. VLSI (GLSVLSI) 309–313 (ACM, 2022).

Fischer, T. et al. Experimental prototype of a spin-wave majority gate. Appl. Phys. Lett. 110, 152401 (2017).

Kanazawa, N. et al. The function of Snell’s regulation for a magnonic majority gate. Sci. Rep. 7, 1–8 (2017).

Talmelli, G. et al. Reconfigurable submicrometer spin-wave majority gate with electrical transducers. Sci. Adv. 6, 4042–4060 (2020). This text presents an experimental demonstration of spin wave logic.

Mahmoud, A. N. et al. Spin wave normalization towards all magnonic circuits. IEEE Trans. Circuits Syst. I 68, 536–549 (2021).

Wang, Q. et al. A magnonic directional coupler for built-in magnonic half-adders. Nat. Electron. 3, 765–774 (2020).

Vanderveken, F. et al. Lumped circuit mannequin for inductive antenna spin-wave transducers. Sci. Rep. 12, 1–13 (2022).

Mitrofanova, A., Safin, A., Kravchenko, O., Nikitov, S. & Kirilyuk, A. Optically initialized and current-controlled logical component primarily based on antiferromagnetic-heavy steel heterostructures for neuromorphic computing. Appl. Phys. Lett. 120, 072402 (2022).

Yang, Q. et al. Realization of excessive spin injection by means of chiral molecules and its utility in logic gadget. IEEE Electron. System Lett. 43, 1862–1865 (2022).

Arava, H. et al. Computational logic with sq. rings of nanomagnets. Nanotechnology 29, 265205 (2018).

Rakheja, S., Flatté, M. E. & Kent, A. D. Voltage-controlled topological spin swap for ultralow-energy computing: efficiency modeling and benchmarking. Phys. Rev. Appl. 11, 054009 (2019).

Allwood, D. A. et al. Magnetic domain-wall logic. Science 309, 1688–1692 (2005).

Luo, Z. et al. Present-driven magnetic domain-wall logic. Nature 579, 214–218 (2020).

Perricone, R. et al. An power environment friendly non-volatile flip-flop primarily based on CoMET know-how. In Design, Automation & Check in Europe Conf. Exhibition (DATE) 390–395 (IEEE, 2019).

Friedman, J. S. et al. Cascaded spintronic logic with low-dimensional carbon. Nat. Commun. 8, 15635 (2017).

Khokhriakov, D. et al. Multifunctional spin logic operations in graphene spin circuits. Phys. Rev. Appl. 18, 64063 (2022).

Pan, C. & Naeemi, A. An expanded benchmarking of beyond-CMOS units primarily based on Boolean and neuromorphic consultant circuits. IEEE J. Explor. Stable-State Comput. Gadgets Circuits 3, 101–110 (2017). This work expands the benchmarking framework for spintronic logic by contemplating each Boolean and non-Boolean circuits and by including new units equivalent to three magnetoelectric units and new flavours of all-spin logic and charge-coupled spin logic.

This articles is written by : Nermeen Nabil Khear Abdelmalak

All rights reserved to : USAGOLDMIES . www.usagoldmines.com

You can Enjoy surfing our website categories and read more content in many fields you may like .

Why USAGoldMines ?

USAGoldMines is a comprehensive website offering the latest in financial, crypto, and technical news. With specialized sections for each category, it provides readers with up-to-date market insights, investment trends, and technological advancements, making it a valuable resource for investors and enthusiasts in the fast-paced financial world.